本文

FPGA/SoCによる組込みRTOSタスクトレーサIPの開発

武田 有志[発表者]、岡部 忠、仲村 将司(情報技術グループ) 、佐藤 研(電子・機械グループ)

1.はじめに

近年の組込みシステムでは、EthernetやUSB等の通信処理に対してRTOS(Real-Time OS)を利用した開発が行われている。タスク実行の把握にはタスクトレースが有用であり、その実現にはOSのサービスコールに対するソフト的なフックが数多く見られる。しかし、この方法では、フック挿入/除去によって実行時間が変化するため、時間制約の厳しい通信システムの検証には不向きである。また、FPGA/SoCではマルチコア化が進められており、FPGA/SoC+RTOS環境下での膨大なトレースデータを抑える仕組みが今後不可欠になると予想される。そこで、本研究では、これらを解決するトレーサIPを開発した。

2.トレーサIPの構成

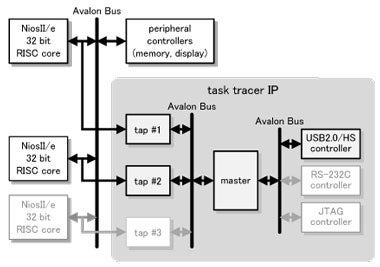

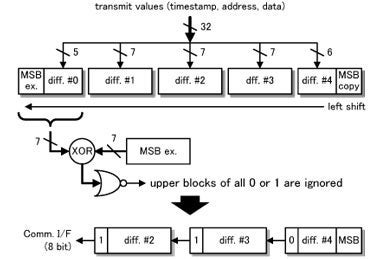

図1は、トレーサIPの構成を示している。Altera社の汎用バスAvalon Busには複数コア(NiosII/e)が接続されており、他方でコアのアドレス/データバスにはトレーサIPが接続されている。トレーサIPは、バススヌーピング方式を採用しており、コアに対してトレース処理の負荷がかからないように構成されている。トレーサIPは、コア各々に対する複数タップと1つのマスタ、そして、トレースデータを送信するUSB2.0通信I/Fから成る。タップではコアがTCB(Task Control Block)にアクセスした際をトリガとしてトレースデータを取得する。マスタでは取得された前回データと新データとの差分を取り、すべて0もしくは1となる上位データを送信しないことでデータ圧縮を実現する(図2)。

図1 トレーサIPの構成

図2 トレースデータの圧縮

3.結果・考察

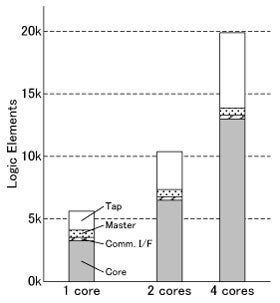

対応可能なコア数についてデータ量とハードウェア量で評価する。タスク遷移間における最大のトレース数は、87.3トレース/msecであった。1トレースは16バイトで構成されており、転送速度は1コア当たり11.2 Mbps必要である。今回使用したUSB2.0チップ(FT2232H)は最大220Mbpsであることから、19.6コアまで対応できる。さらに図2の圧縮を有効にすると、データ量は45.2%削減された。図3はハードウェア使用量を示しており、20k LEの回路規模を有するFPGAでは、4コアまで対応できる。

図3 コアに対するハードウェア使用量

4.まとめ

本IPは、マルチコア対応かつコア負荷がゼロであることを特徴とする。今後、組込みシステムは高信頼化が求められると予想される。本IPは、こうした分野への導入が期待される。